新書推薦:

《

何以中国·何谓唐代:东欧亚帝国的兴亡与转型

》

售價:HK$

89.7

《

一间只属于自己的房间 女性主义先锋伍尔夫代表作 女性精神独立与经济独立的象征,做自己,比任何事都更重要

》

售價:HK$

45.8

《

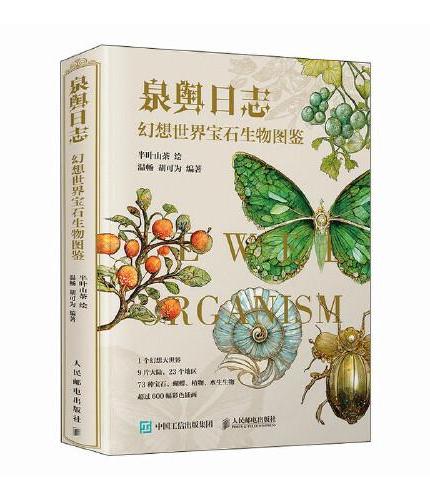

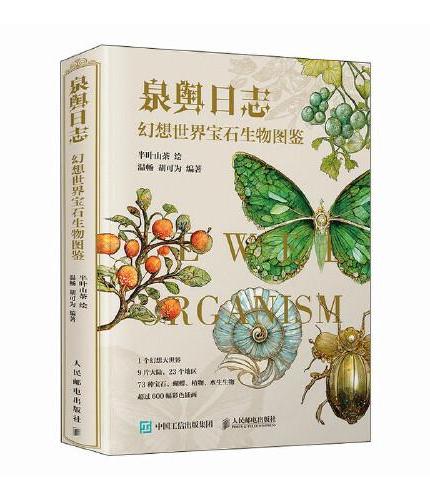

泉舆日志 幻想世界宝石生物图鉴

》

售價:HK$

137.8

《

养育女孩 : 官方升级版

》

售價:HK$

51.8

《

跨界:蒂利希思想研究

》

售價:HK$

109.8

《

千万别喝南瓜汤(遵守规则绘本)

》

售價:HK$

45.9

《

大模型启示录

》

售價:HK$

115.0

《

东法西渐:19世纪前西方对中国法的记述与评价

》

售價:HK$

207.0

|

| 內容簡介: |

《普通高等教育“十二五”电子信息类规划教材:基于Quartus

II的CPLD的数字系统设计与实现》是山东省精品课程“电子技术”的配套教材之一,第1章介绍了QuartusⅡ9?X的开发流程,第2章介绍了CPLD的相关知识,第3章介绍门电路的实现方法,第4章介绍组合逻辑电路,第5章介绍了组合逻辑电路的应用,第6章介绍了触发器的知识,第7章介绍了时序逻辑电路,第8章介绍了时序逻辑电路的设计及应用,第9章是基于原理图的综合设计实例,第10章是基于混合输入的综合设计。

《普通高等教育“十二五”电子信息类规划教材:基于Quartus

II的CPLD的数字系统设计与实现》可作为高等院校自动化、电子信息、计算机及其他相关专业的教材,也可供从事电子设计的工程技术人员参考。

|

| 目錄:

|

前言

第1章 QuartusⅡ9.X开发流程

1.1 QuartusⅡ概述

1.2 面向FPGACPLD的开发流程

1.2.1 设计输入

1.2.2 综合

1.2.3 布线布局(适配)

1.2.4 仿真

1.2.5 下载和硬件测试

1.3 QuartusⅡ操作流程

1.3.1 创建工程

1.3.2 设计文件输入

1.3.3 编译前设置

1.3.4 全程编译

1.3.5 时序仿真

1.3.6 RTL级电路

1.3.7 引脚锁定

1.3.8 编程下载

1.3.9 其他下载方式

1.4 QuartusⅡ9.X的使用

1.4.1 原理图电路设计方法

1.4.2 层次化设计流程

第2章 CPLD简介

2.1 基本PLD的原理及分类

2.1.1 PLD的原理概述

2.1.2 PLD的分类

2.2 CPLD的结构与原理

2.2.1 逻辑阵列块

2.2.2 宏单元

2.2.3 扩展乘积项

2.2.4 可编程连线阵列

2.2.5 IO控制模块

2.3 数字电路设计的常用外围模块电路

2.3.1 秒信号发生电路

2.3.2 单脉冲产生电路

2.3.3 电平保持产生电路

2.3.4 指示灯电路

2.3.5 数码管显示电路

2.3.6 矩阵键盘

2.3.7 发声电路

2.4 数字电路设计的其他辅助电路

2.4.1 电源电路

2.4.2 复位电路

2.4.3 时钟电路

第3章 门电路

3.1 基本门电路

3.1.1 与逻辑

3.1.2 或逻辑

3.1.3 非逻辑

3.2 复合逻辑电路

3.2.1 与非逻辑电路

3.2.2 或非逻辑电路

3.2.3 异或逻辑电路

3.2.4 同或逻辑电路

3.2.5 与或非逻辑电路

第4章 组合逻辑电路

4.1 加法器

4.1.1 半加器

4.1.2 全加器

4.1.3 4位串行进位加法器

4.1.4 4位超前进位加法器

4.2 比较器

4.2.1 1位比较器

4.2.2 4位扩展比较器

4.3 编码器

4.3.1 二进制编码器

4.3.2 8线?3线扩展优先编码器

4.3.3 其他编码器

4.4 译码器

4.4.1 二进制译码器

4.4.2 3位二进制扩展译码器

4.4.3 显示译码器

4.5 数据选择器

4.5.1 4选1数据选择器

4.5.2 字扩展数据选择器

4.5.3 位扩展数据选择器

4.6 数据分配器

4.6.1 1路?4路数据分配器

4.6.2 数据分配器的扩展

第5章 组合逻辑电路应用

5.1 组合逻辑电路的设计与测试方法

5.1.1 组合逻辑电路的一般设计

方法

5.1.2 组合逻辑电路的测试方法

5.2 加法器应用

5.3 比较器应用

5.4 编码器应用

5.4.1 16线?4线优先编码器

5.4.2 医院呼叫灯的控制电路

5.5 译码器应用

5.5.1 4线?16线二进制译码器

5.5.2 设计一个编码信号显示电路

5.6 数据选择器应用

5.7 竞争冒险

5.7.1 险象的判断

5.7.2 险象的解决方法

第6章 触发器

6.1 基本触发单元

6.1.1 基本触发器

6.1.2 同步触发器

6.1.3 边沿触发器

6.2 触发器之间的转换

6.2.1 JK触发器转换成其他触发器

6.2.2 D触发器转换成其他触发器

第7章 时序逻辑电路

7.1 同步二进制计数器

7.1.1 同步3位二进制加减法计数器

7.1.2 同步3位二进制可逆计数器

7.1.3 带控制同步4位二进制加法可逆计数器

7.2 异步二进制计数器

7.2.1 二进制异步加减法计数器

7.2.2 二进制扩展异步计数器

7.3 十进制计数器

7.3.1 同步十进制加减法计数器

7.3.2 同步十进制可逆计数器

7.3.3 带控制1位同步十进制加法计数器

7.3.4 单双时钟1位同步十进制可逆计数器

7.4 基本寄存器

7.5 移位寄存器

7.5.1 单向移位寄存器

7.5.2 双向移位寄存器

7.5.3 8位移位寄存器

7.6 移位寄存器型计数器

7.6.1 环形计数器

7.6.2 扭环形计数器

第8章 时序逻辑电路的设计及应用

8.1 时序逻辑电路的设计与测试方法

8.1.1 时序逻辑电路的一般设计方法

8.1.2 同步时序逻辑电路的设计步骤和方法

8.1.3 时序逻辑电路的测试方法

8.2 N进制计数器

8.2.1 二十四进制计数器

8.2.2 六十进制计数器

8.3 时序逻辑电路的应用

8.3.1 计数器的应用

8.3.2 异步计数器的应用

8.3.3 简易数字秒表的设计

8.3.4 简易数字钟的设计

第9章 基于原理图的综合设计实例

9.1 数字频率计

9.2 交通灯控制电路

9.3 电风扇控制电路

9.4 跑马灯设计

9.5 洗衣机控制器

第10章 基于原理图和VHDL混合输入的综合设计实例

10.1 篮球比赛进攻24s计时器

10.2 出租车自动计费器

10.3 电梯控制器

10.4 4×4键盘扫描电路设计

附录实验系统原理图和实验系统

实物图

参考文献

|

|