新書推薦:

《

先进电磁屏蔽材料——基础、性能与应用

》

售價:HK$

221.8

《

可转债投资实战

》

售價:HK$

99.7

《

王氏之死(新版,史景迁成名作)

》

售價:HK$

54.9

《

敢为天下先:三年建成港科大

》

售價:HK$

77.3

《

长高食谱 让孩子长高个的饮食方案 0-15周岁儿童调理脾胃食谱书籍宝宝辅食书 让孩子爱吃饭 6-9-12岁儿童营养健康食谱书大全 助力孩子身体棒胃口好长得高

》

售價:HK$

47.0

《

身体自愈力:解决内在病因的身体智慧指南

》

售價:HK$

98.6

《

非言语沟通经典入门:影响人际交往的重要力量(第7版)

》

售價:HK$

123.1

《

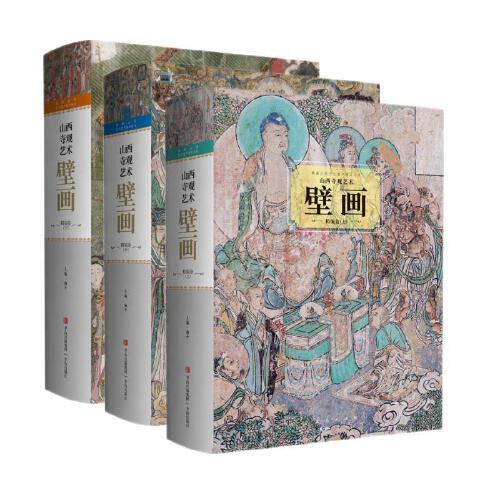

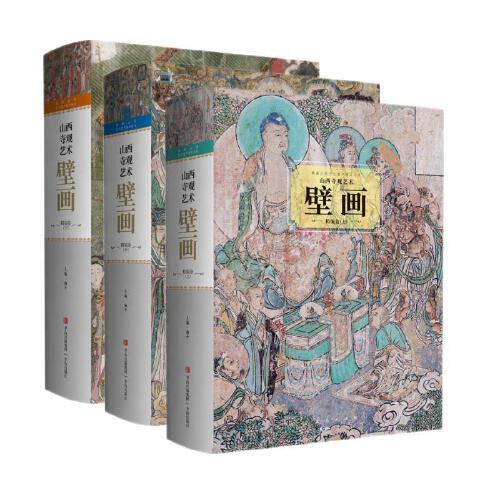

山西寺观艺术壁画精编卷

》

售價:HK$

1680.0

|

| 編輯推薦: |

|

《FPGA技术开发附光盘高级篇》系统地介绍了利用EDA软件开发FPGA的基本流程,FPGA高级开发技术以及FPGA发展的趋势等。全书共分为7章。本书可作为从事FPGA、数字信号处理以及相关技术设计研究人员的参考书籍,同时也可以作为高校自动化、电子信息、信号处理、通信系统等相关专业本科生、研究生的教材或者参考资料。本书由李洪涛对全书进行了统稿。

|

| 內容簡介: |

《FPGA技术开发附光盘高级篇》系统介绍了

利用EDA软件开发FPGA的基本流程,FPGA高级开发技 术以及FPGA发展的趋势等。全书内容主要包括第三方

EDA软件介绍;xilinx公司开发软件ISE简介;利用 嵌入式逻辑分析仪调试FPGA的方法与技巧;FPGA底层

开发技术——源语、约束与伪指令的设计;对Xilinx 公司IP软核与嵌入式硬件资源的介绍;结合开发实例

详细介绍FPGA在通信系统中的应用等。

本书第1章到第3章介绍利用EDA软件开发、调试

FPGA的基本流程,第4章介绍源语、约束与伪指令等 FPGA高级开发技术;第5章介绍利用IP软核简化FPGA

设计的方法;第6章介绍FPGA发展的趋势——嵌入式 硬件资源;第7章介绍FPGA在通信系统中的应用以及 开发实例。

《FPGA技术开发附光盘高级篇》内容丰富、

结构合理、图文并茂,便于实施系统教学。本书可以 作为高等工科院校电类专业的教学用书,也可用于自

学或供工程技术人员参考。本书由李洪涛对全书进行 了统稿。

|

| 目錄:

|

第1章 第三方EDA工具

1.1 Modelsim及其应用——前仿真、后仿真的作用与区别

1.1.1 仿真的意义与Modelsim软件

1.1.2 测试向量

1.1.3 利用Modelsim进行仿真

1.2 Synplify/Synplify Pro及其应用

1.2.1 Synplify/Synplify Pro简介

1.2.2 利用Synplify/Synplify

Pro进行综合设计与约束的设定

1.3 Debussy及其应用

1.3.1 Debussy简介

1.3.2 利用Debussy进行调试

习题

第2章 Xilinx开发设计软件ISE介绍——厂商的开发软件

2.1 ISE开发软件简介

2.2 ISE开发流程

2.2.1 新建项目

2.2.2 选择器件

2.2.3 添加源文件

2.2.4 引脚分配

2.2.5 项目执行

2.2.6 配置bit文件

2.3 综合与实现Synthesize-XST and Implement Design

2.3.1 Synthesize-XSTXilinx Synthesis

Technology

2.3.2 Implement Design

2.4 利用ISE软件对E2pROM的配置

习题

第3章 嵌入式逻辑分析仪的应用——一种高级的调试手段

3.1 嵌入式逻辑分析仪的意义

3.2 Xilinx公司的嵌入式逻辑分析仪ChipScope Pro

3.2.1 Chipscope Pro简介

3.2.2 Chipscope Pro的构成

3.2.3 Chipscope Pro设计流程

习题

第4章 伪指令、源语与约束设计——FPGA高级设计

4.1 伪指令、源语与约束的意义

4.1.1 伪指令

4.1.2 源语

4.1.3 约束

4.2 伪指令——Xilinx 中伪指令的设计

4.2.1 Xilinx中的编译伪指令

4.2.2 Xilinx扣的综合伪指令

4.3 源语——Xilinx中源语的设计

4.3.1 Xilinx中的源语

4.3.2 源语设计实例

4.4 约束——Xilinx和约束的设计

4.4.1 Xilinx户的约束文件

4.4.2 约束设计实例

习题

第5章 IP软核的设计——简化设计的一种方法

5.1 FPGA的p软核简介

5.1.1 IP软核简介

5.1.2 IP软核生成器

5.2 移位寄存器IP软核

5.2.1 模块简介

5.2.2 模块特点

5.2.3 模块模型

5.2.4 配置方式

5.3 8B/10B编解码软核

5.3.1 模块简介

5.3.2 算法原理

5.3.3 模块特点

5.3.4 功能模块

5.3.5 配置方式

5.4 CORDIC算法IP软核

5.4.1 算法简介

5.4.2 算法原理

5.4.3 模块特点

5.4.4 引脚定义

5.4.5 配置方式

5.5 DDS算法IP软核

5.5.1 模块简介

5.5.2 算法原理

5.5.3 模块特点

5.5.4 配置方式

5.6 PCI接口IP软核

5.6.1 接口简介

5.6.2 模块特点

5.6.3 总线命令与时序

5.6.4 配置方式

5.7 DDR Ⅱ接口IP软核

5.7.1 DDR Ⅱ简介

5.7.2 模块特点

5.7.3 硬件框图

5.7.4 配置方式

习题

第6章 嵌入式硬件资源——FPGA的发展趋势之一

6.1 嵌入式硬件资源的发展现状

6.2 DSP资源

6.2.1 嵌入式DSP简介

6.2.2 DSP48 Tile简介

6.2.3 DSP48 Slice模型

6.3 时钟及锁相环资源

6.3.1 时钟及锁相环简介

6.3.2 锁相环

6.3.3 时钟管理器

6.3.4 时钟管理模块

6.4 存储器资源

6.4.1 嵌入式存储器简介

6.4.2 Block RAM特点

6.4.3 Block RAM端口模型

6.5 高速收发器资源

6.5.1 SERDES技术简介

6.5.2 SERDES接口组成

6.5.3 GTX/GTP结构

6.6 以太网MAC资源

6.6.1 以太网MAC简介

6.6.2 以太网MAC结构

6.6.3 接口配置

6.7 嵌入式处理器PowerPC资源

6.7.1 嵌入式PowerPC简介

6.7.2 PowerPC硬件结构

6.7.3 PowerPC的总线接口

6.7.4 PowerPC指令集

6.8 可扩展处理平台-Zynq系列

6.8.1 可扩展处理平台简介

6.8.2 Zynq系列硬件结构

6.8.3 Zynq系列资源

6.8.4 Zynq开发流程

习题

第7章 FPGA在通信系统中的应用

7.1 M序列发生器的FPGA设计实例

7.1.1 M序列的特点及应用

7.1.2 M序列产生的原理

7.1.3 利用FPGA设计M序列发生器

7.1.4 Modelsim仿真与Chipscope调试

7.2 DDS直接频率合成器的FPGA设计实例

7.2.1 DDS基本原理及性能特点

7.2.2 DDS的工作原理

7.2.3 利用FPGA设计DDS直接频率合成器

7.2.4 Modelsim仿真与Chipscope调试

7.3 循环冗余校验CRC的FPGA设计实例

7.3.1 循环冗余校验CRC的基本原理及性能特点

7.3.2 CRC的实现方法

7.3.3 利用FPGA设计循环冗余校验CRC

7.3.4 Modelsim仿真与Chipscope调试

7.4 MDIO接口的FPGA设计实例

7.4.1 PHY芯片及MDIO接口简介

7.4.2 利用FPGA设计MDIO接口

7.4.3 Modelsim仿真与Chipscope调试

7.5 MAC接口的FPGA设计实例

7.5.1 MAC接口的基本原理及应用

7.5.2 利用FPGA设计MAC接口

7.5.3 Modelsim仿真与chipscope调试

习题

参考文献

|

|